一、有源晶振与无源晶振的比较

无源晶振:就是一个晶体,自己不能够振荡,依附配合其他IC内部振荡电路工作。

有源晶振:晶体+振荡电路,封装在一起。给他供上电源,就有波形输出。

1、无源晶体——无源晶体需求用DSP片内的振荡器,在datasheet上有建议的衔接手段。

无源晶体没有电压的问题,信号电平是可变的,也就是说是依据起振电路来决定的,相同的晶体能够实用于多种电压;

可用于多种不一样时钟信号电压要求的DSP,并且价钱通常也较低,所以关于普通的应用假如要求允许建议用晶体,这特别适合于产品线丰富批量大的生产者。

无源晶体有关于晶振而言其缺陷是信号质量较差,通常需求准确配套外围电路(用于信号配套的电容、电感、电阻等);

更改不一样频率的晶体时周边配置电路需求做相应的调整。建议采取精度较高的石英晶体,尽量不要采取精度低的陶瓷小心。

2、有源晶振——有源晶振不需求DSP的内部振荡器,信号质量好,比较稳固;

并且衔接方法相比较简单(主如果做好电源滤波,通常应用一个电容和电感组成的PI型滤波网络,输出端用一个小阻值的电阻过滤信号便可),不需求复杂的配置电路。

有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。有关于无源晶体,有源晶振的缺陷是其信号电平是固定的,需求选择好适合输出电平,灵巧性较差,并且价钱高。

关于时序要求敏感的应用,个人以为还是有源的晶振好,缘由是能够选用比较精准的晶振,甚至是高级的温度赔偿晶振。

有些DSP内部没有起振电路,只能应用有源的晶振,如TI的6000系列等。有源晶振对比于无源晶体通常体积较大,但目前许多有源晶振是表贴的,体积和晶体相当,有的甚至比许多晶体还要小。

几点留意事项:

1、需求倍频的DSP需求配置好PLL周边配置电路,主如果隔离和滤波;

2、20MHz以下的晶体晶振基本上都是基频的器件,稳固度好,20MHz以上的大多是谐波的(如3次谐波、5次谐波等等);

稳固度差,所以强烈建议应用低频的器件,毕竟倍频用的PLL电路需求的周边配置主如果电容、电阻、电感,其稳固度和价钱方面远远好过晶体晶振器件;

3、时钟信号走线长度尽量短,线宽尽量大,与其它印制线间距尽量大,紧靠器件布局布线,必要时能够走内层,和用地线包抄;

4、通过背板从外部引入时钟信号时有特别的设计要求,需求详细参考有关的资料。

另外还要做一些说明:

整体来讲晶振的稳固度等方面好过晶体,特别是精准丈量等领域,绝大大部分用的都是高级的晶振,这样便能够把各类赔偿技术集成在一起,削减了设计的复杂性。

试想,假如采取晶体,然后自己设计波形整形、抗搅扰、温度赔偿,那样的话设计的复杂性将是什么样的呢?

我们这里设计射频电路等对时钟要求高的场所,就是采取高精度温补晶振的,工业级的要好几百元一个。

特别领域的应用假如找不到适合的晶振,也就是说设计的复杂性超过了市场上制品晶振水平,就必须自己设计了,这类情形下就要选用晶体了,可是这些晶体确定不是市场上的普通晶体,而是特别的高端晶体,如红宝石晶体等等。

更高要求的领域情形更特别,我们这里在高精度测试时采取的时钟甚至是原子钟、铷钟等设备提供的,通过专用的射频接插件衔接,是个大型设备,相当粗笨 ... ...

1.有源晶振与无源晶振的差别

无源晶振为crystal(晶体)无源晶振是有2个引脚的无极性元件,需求借助于时钟电路才能够产生振荡信号,本身没办法振荡起来;

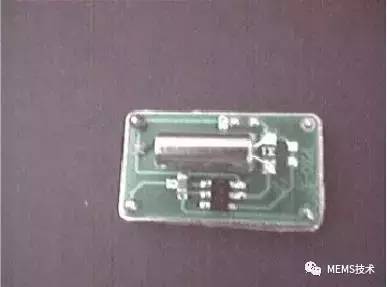

有源晶振则叫做oscillator(振荡器)。有源晶振有4只引脚,是一个完整的振荡器,其中除过石英晶体外,还有晶体管和阻容元件,所以体积较大。

2.无源晶振和有源晶振的优缺陷

无源晶体有关于晶振而言其缺陷是信号质量较差,通常需求准确配套外围电路(用于信号配套的电容、电感、电阻等),更改不一样频率的晶体时周边配置电路需求做相应的调整。

建议采取精度较高的石英晶体,尽量不要采取精度低的陶瓷小心。

有关于无源晶体,有源晶振的缺陷是其信号电平是固定的,需求选择好适合输出电平,灵巧性较差,并且价钱高。

关于时序要求敏感的应用,个人以为还是有源的晶振好,缘由是能够选用比较精准的晶振,甚至是高级的温度赔偿晶振。

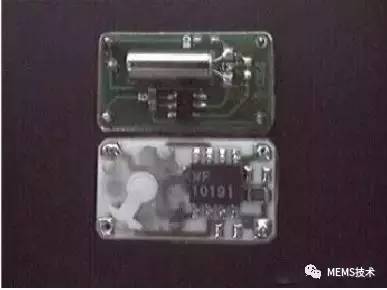

二、有源晶振的管脚

无源晶振两个管脚能够随便。

有源晶振依据封装不一样,管束排列不一样(打点的为“1脚”,逆时钟看)

有个点标志的为1脚,按逆时针(管脚向下)分别为2、3、4。

有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。

方形有源晶振引脚散布:

1、正方的,应用DIP-8封装,打点的是1脚。

1-NC; 4-GND; 5-Output; 8-VCC

2、长方的,应用DIP-14封装,打点的是1脚。

1-NC; 7-GND; 8-Output; 14-VCC

BTW:

1、电源有两种,一种是TTL,只能用5V,一种是HC的,能够3.3V/5V

2、边缘有一个是尖角,三个圆角,尖角的是一脚,和打点一致。

Vcc out

NC(点) GND

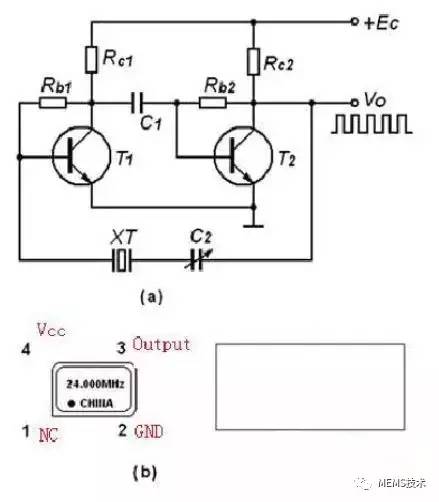

三、有源晶振内部构造

能够看到有源晶振 = 普通晶振 + 逻辑电路

四、有源晶振的输出波形

无源晶振输出正弦波。

有源晶振输出正弦波或方波。

假若有源晶振把整形电路做在有源晶振里面了的话,输出就是方波,但许多时候在示波器上看到的还是波形不太好的正弦波,这是因为示波器的带宽不够;

似乎有源晶振20MHz,假如用40MHz或60MHz的示波器丈量,显示的是正弦波,这是因为方波的傅里叶分解为基频和奇次谐波的叠加,带宽不够的话,就只剩下基频20MHz和60MHz的谐波;

所以显示正弦波。完美的再现方波需求起码10倍的带宽,5倍的带宽只能算是委曲,所以需求起码100M的示波器。

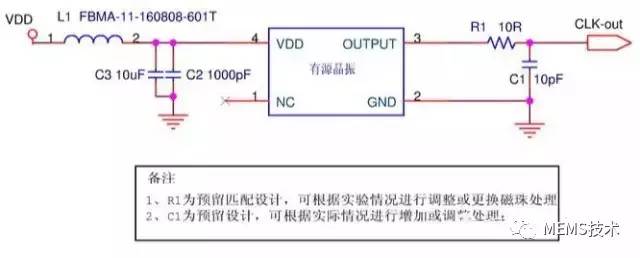

五、有源晶振的典范电路

如上图,为有源晶振EMC标准设计电路,假如对EMC要求不高,能够去掉L1,及C1。只保存电源输入端的去耦电容,取0.1uf便可,输出端保存输出电阻,约10到27欧姆。

说明:

1.电源端磁珠L1与电容C2,C3组成lc滤波电路。

2.关于输出端串连的电阻的用处。

串电阻是为了减小反射波,防止反射波叠加引发过冲。有时,不一样批次的板子特征不一样,留个电阻地位便于调整板子状态到最好。如无必要串电阻,就用0欧电阻衔接。

详细用处以下:

1、能够削减谐波,有源晶体输出的是方波,这将引发谐波搅扰,特别是阻抗严重不配套的情形下,加上电阻后,该电阻将与输入电容组成RC积分腻滑电路,将方波转换为近似正弦波;

尽管信号的完整性遭到必定影响,但因为该信号还要经事后级缩小、整形后才作为时钟信号,所以,性能其实不受影响,该电阻的大小需求依据输入端的阻抗、输入等效电容,有源晶体的输出阻抗等因素选择。

2、能够进行阻抗配套,减小回波搅扰及致使的信号过冲。我们晓得,只需阻抗不配套,都产生信号反射,即回波,有源晶体的输出阻抗通常都很低,普通在几百欧以下;

而信号源的输入端在芯片内部构造上通常是运放的输入端,由芯片的内部电路与外部的无源石英晶体组成谐振电路(应用有源晶体后就不需求这个晶体了),这个运放的输出阻抗都在兆欧以上。

普通这个输出电阻能够串27欧姆左右。

郑重声明:此文内容为本网站转载企业宣传资讯,目的在于传播更多信息,与本站立场无关。仅供读者参考,并请自行核实相关内容。